伟芯科技ESD知识分享——静电放电的测试

伟芯科技(绍兴)有限公司,绍兴集成电路小镇已入住的专业的集成电路静电保护(ESD)技术和IP产品提供商,在ESD保护业务领域积累了丰富的理论基础和实战案例,成功解决了大规模SOC产品、多电源域多管脚产品、RF高频产品、高压产品和finfet等产品的ESD可靠性问题。为广大集成电路企业客户提供ESD IP库开发、全芯片ESD保护方案、ESD失效分析和改进方案、ESD专利授权等产品和服务。

在伟芯官网中,我们将教导您有关集成电路的ESD知识,并介绍集成电路的 ESD 规格标准以及集成电路产品的ESD测试方法;再来,我们将教导您有关集成电路的各种ESD防护设计,其相关技术含括制程 (Process)、元件(Device)、电路 (Circuits) 、系统 (Systems) 、以及测量(Measurement) 。这些相关技术的介绍及设计实例的说明,必能协助您解决贵公司集成电路产品所遭遇到的 ESD问题

第三章 静电放电的测试

|

在了解静电放电的模式后,正本清源的工作只做了一 半,接下来必需了解静电放电如何影响IC内部,而静电放 电电流如何在IC中流窜是有一脉络可循,针对各pin间做交 叉放电分析是最基本的测试方式,但并非胡乱交叉测试就 能得到结论,必需有一套正确而快速的测试方法做为测试 的准则。但IC对静电有一定的承受能力,想得知IC的静电 耐受力,在做测试分析时需有一套正确的判断标准,否则 光有测试方法而无判读方法也徒枉然。在本章中,将对静 电放电的测试及判读做一介绍。 |

3.1 静电放电测试组合

3.1.1 I/O Pin的静电放电测试

静电的累积可能是正的或负的电荷,因此静电放电测试对同一IC脚而言是具有正与负两种极性。对每一I/O ( Input or Output) Pin而言,HBM与MM静电放电对IC的放电,有下列四种ESD测试组合,其等效电路示意图如图3.1-1所示。

图3.1-1 I/O Pin 的静电放电测试组合 (下页)

1. PS-mode:VSS脚接地,正的ESD电压出现在该I/O 脚对VSS脚放电,此时VDD与其它脚皆浮接;

2. NS-mode:VSS脚接地,负的ESD电压出现在该I/O 脚对VSS脚放电,此时VDD与其它脚皆浮接;

3. PD-mode:VDD脚接地,正的ESD电压出现在该I/O 脚对VDD脚放电,此时VSS与其它脚皆浮接;

4. ND-mode:VDD脚接地,负的ESD电压出现在该I/O 脚对VDD脚放电,此时VDD与其它脚浮接。

3.1.2 Pin-to-Pin的静电放电测试

但静电放电可能出现在IC的任何两只脚之间,若该两只脚之间无直接的相关电路,唯一共同使用的是VDD与VSS电源线相连接。ESD发生在不相干的两支IC脚之间时,静电放电电流会先经由某部份的电路跑到VDD或VSS电源线上,再由VDD或VSS电源连接线跑到另一支IC脚,再由那支IC脚流出IC之外。若每一IC的每两脚之间都要做测试,那么一颗40 pin的IC便要有1560种排列组合的ESD测试,这太浪费测试时间。因此,改良式的测试方法如图3.1-2 所示,即所谓的Pin-to-Pin 测试。在该Pin-to-Pin 测试组合中 ,亦由于静电放电的正负极性而分成两种测试模式 :

图3.1-2 Pin-to-Pin 的静电放电测试组合

1. Positive-mode:正的ESD电压出现在某一I/O 脚,此时所有其它I/O 脚皆一起接地,但所有的VDD脚

与VSS脚皆浮接;

2. Negative-mode:负的ESD电压出现在某一I/O 脚,此时所有其它I/O 脚皆一起接地,但所有的VDD脚与VSS脚皆浮接。

3.1.3 VDD-to-VSS的静电放电测试

静电放电也可能发生在VDD脚与VSS脚之间,因此对VDD脚与VSS脚有下列的ESD测试组合,其等效电路示意图如图3.1-3所示。

图3.1-3 VDD-to-VSS 的静电放电测试组合

1. Positive-mode:正的ESD电压出现在VDD脚,此时VSS脚接地, 但所有I/O 脚皆浮接;

2. Negative-mode:负的ESD电压出现在VDD脚,此时VSS脚接地, 但所有I/O 脚皆浮接。

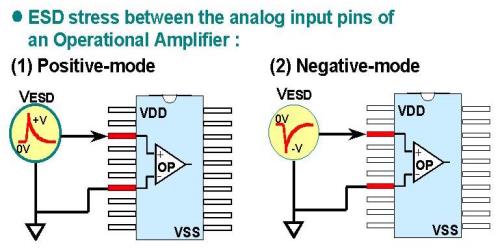

3.1.4 Analog Pin的静电放电测试

在模拟(Analog) IC内常有差动输入级(Differential Pair) ,例如运算放大器(OP AMP) 的输入级,如果该差动输入级的正负输入端都连接到IC的Pin时,这两支输入脚要另外单独做静电放电测试,以验证该两支输入脚所连接的差动输入级会不会被静电放电所破坏,其等效电路示意图如图3.1-4所示。

图3.1-4 Analog Pin 的静电放电测试组合

1. Positive-mode:正的ESD电压出现在差动输入级的正输入脚位,此时差动输入级的负输入脚接地, 但其它所有I/O 脚以及VDD与VSS脚皆浮接;

2. Negative-mode:负的ESD电压出现在差动输入级的正输入脚位, 此时差动输入级的负输入脚接地, 但其它所有I/O 脚以及VDD与VSS脚皆浮接。

3.1.5 CDM的静电放电测试

由于组件充电模式(CDM)的静电放电机制与前述的HBM及MM 放电机制不同,因此CDM的静电放电测试如图3.1-5所示。首先,静电电压被充入该集成电路的基体之中,并储存在其基体之中,为避免充电过程造成IC损伤,因此充电电压必须经由一高电阻值(10MΩ以上)的限流电阻对IC基体充电,对P型基体之IC而言,VSS脚位是含连接到其基体,因此该充电电压是经由该限流电阻对IC的VSS脚充电。当IC充电之后,IC本身即便带有正极性的或负极性的电压,该IC的其它脚位(包括Input, Output,,I/O, 以及VDD脚位)再分别接地放电,以完成CDM的静电 放电测试。由脚位接地放电的方式,CDM又可分为 socketed以及non-socketed两种,其中socketed的CDM放电 是指该脚位接地放电时是经由IC插座与relay开关而接地的 。而non-socketed的CDM放电是把带电的IC在浮接状态下,经由放电探棒(discharge bar)而直接接地放电。这两种放电方式的CDM测试机台都已有商业产品在销售。

图3.1-5 组件充电模式的静电放电测试组合

1. Positive-mode:整颗IC处于浮接状态, IC的基体(Substrate)先被充电而具有正极性的电压,然后该 IC的任一脚位以直接接地的方式放电;

2. Negative-mode:整颗IC处于浮接状态, IC的基体(Substrate)先被充电而具有负极性的电压,然后该 IC的任一脚位以直接接地的方式放电。

3.2 静电放电测试方式

在每一测试模式下,IC的该测试脚先被打上(Zap)某一ESD电压,而且在同一ESD电压下,IC的该测试脚必须要被Zap三次,每次Zap之间的时间间隔约一秒钟,Zap三次之后再观看该测试脚是否己被ESD所损坏,若IC尚未被损坏则调升ESD的电压,再Zap三次。此ESD电压由小而逐渐增大,如此重复下去,直到该IC脚己被ESD所损坏,此时造成IC该测试脚损坏的ESD测试电压称为『静电放电故障临界电压 (ESD failure threshold)』。

如果每次调升的ESD测试电压调幅太小,则测试到IC脚损坏要经过多次的ESD放电,增长测试时间; 若每次调升的ESD测试电压太大,则难以较精确测出该IC脚的ESD耐压能力。因此,有一测试经验法则如表3.2-1所示,当ESD测试电压低于1千伏特时,每次ESD电压增加量为50V(或100V);当ESD测试电压高于1千伏特时,每次ESD电压增加量为100V(或250V)。而ESD测试的起始电压则从平均ESD故障临界电压的70%开始。

表3.2-1 ESD 测试法则

|

(1). Stress number = 3 Zaps. (5 Zaps, the worst case) |

|

|

(2). Stress step |

ΔVESD = 50V(100V) for VZAP <=1000V |

|

(3). Starting VZAP = 70% of averaged ESD failure threshold (VESD) |

|

例如,某一IC的人体放电模式(HBM) ESD耐压大概平均在2000V左右,那么起始测试电压约为1400V开始。测试时,1400V的ESD电压 Zap到IC的某一脚去(相对的VDD或VSS脚要接地),测三次1400V的ESD放电,若该IC脚尚未被损坏,则调升ESD电压到1500V,此1500V的ESD电压再打到该IC脚三次,若该IC脚尚未被损坏,则再调升ESD电压到1600V,依此类推,直到该IC脚被静电放电所损坏为止。

我们来估算一下,一颗40pin的IC (38支I/O,1支VDD,1支VSS),其人体放电模式(HBM)自1400V 测到2000V,每次ESD电压增加量为100V的情形下,所要测试的次数 :每一测试脚在变化ESD电压之下的Zap次数= [(2000-1400)/ 100+ 1] ×3=21次;每一支Input/Output脚的测试组合 = 4种 (如图3.1-1所示);38支Input/output脚的总测试次数=38支×4 种×21次= 3192次;Pin-to-Pin 静电放电测试(如图3.1-2所示) 之次数=38支×2种×21次=1596次;VDD-to-VSS静电放电测试(如图3.1-3所示)之次数=1支×2种×21=42次;故该40脚位IC的ESD(1400~2000V)总测试次数= 4830次。

由上述的简单估算可知,一具有40脚位的IC,只从1400V测到2000V,每一次电压调升100V,则要4830次的ESD放电测试。而在实际情形,IC脚的耐压度可能每一支都不相同,要真正测出每一支脚的ESD耐压程度,则所需测试次数会远超过上述的数字。因此适度放宽每次ESD电压调升的幅度(自100V→250V)可以减少测试的次数及时间。

以上所谈的ESD测试次数是指HBM测试,若该IC也要做MM以及CDM的ESD测试,则还要再加上MM及CDM的ESD测试次数。

3.3 静电放电故障判断

IC经由ESD测试后,要判断其是否已被ESD所破坏, 以便决定是否要再进一步测试下去,但是如何判定该IC已被ESD所损坏了呢?常见的有下述三种方法 :

1‧绝对漏电流:当IC被ESD测试后,其Input/Output脚的漏电电流超过1μA(或10μA)。漏电电流会随所加的偏压大小增加而增加,在测漏电电流时所加的偏压有人用5.5V(VDDX1.1),也有人用7V(VDDX1.4)。

2‧相对I-V漂移:当IC被ESD测试后,自Input/Ouput脚看进IC内部的I-V特性曲线漂移量在30% (20%或40%)。

3‧功能观测法: 先把功能正常且符合规格之IC的每一支脚依测试组合打上某一电压准位的ESD测试电压,再拿去测试其功能是否仍符合原来的规格。用不同的故障判定准则,对同一IC而言,可能会有差距颇大的ESD故障临界电压。因此ESD故障临界电压要在有注明其故障判定准则条件之下,才显得有意义!

3.4 静电放电测试结果的判读

表3.4-1 某一IC的ESD测试实际结果(单位 : V)

|

接 地 脚 |

VDD(+) PD-mode |

VDD(-) ND-mode |

VSS(+) PS-mode |

VSS(-) NS-mode |

|

测 试 脚 |

||||

|

2 |

2500 |

-1000 |

500 |

OK |

|

3 |

1750 |

-500 |

500 |

OK |

|

4 |

VDD |

VDD |

VDD |

VDD |

|

5 |

7250 |

OK |

7000 |

OK |

|

6 |

7000 |

OK |

7000 |

OK |

|

7 |

4250 |

-500 |

4000 |

-5750 |

|

8 |

5000 |

-250 |

4500 |

-3000 |

|

9 |

3000 |

OK |

4500 |

-7000 |

|

10 |

OK |

OK |

7500 |

OK |

|

11 |

7250 |

OK |

7250 |

OK |

|

12 |

2000 |

-1000 |

500 |

OK |

|

13 |

2250 |

-750 |

500 |

OK |

|

14 |

2250 |

OK |

750 |

OK |

|

15 |

6500 |

-750 |

500 |

OK |

|

16 |

1500 |

OK |

500 |

OK |

|

17 |

VSS |

VSS |

VSS |

VSS |

表3.4-1为一IC之ESD测试结果,测试脚4是VDD,测试脚17为VSS,其它为Input或Output脚。表中"OK"表示其ESD耐压超过8KV以上。对Input/Output脚有四种测试模式 ,我们看第7脚,其ESD耐压分别为4250V(PD-mode),-500 V(ND-mode),4000V(PS-mode),以及 -5750V(NS-mode),此第7脚的静电放电故障临界电压(ESD failure threshold)定义为其四种测试模式下的最低值,即此第7脚的ESD failure threshold为500V。另外,我们再看第11脚,其ESD耐压分别为7250(PD-mode),超过8000V(ND-mode),7250(PS- mode),以及超过8000V(NS-mode),此第11脚的ESD failure threshold为7250V。依此类推,每一脚都有其ESD failure threshold。而此颗IC的ESD failure threshold定义为所有IC脚中ESD failure threshold最小的那个电压值,因此,该颗IC的ESD failure threshold仅达500V。即使有些脚的ESD耐压可达七千多伏特,这颗IC的静电放电故障临界电压仍定义为500V。

因此,静电放电防护电路的设计,要能够提升IC所有脚位的静电放电故障临界电压,而不是只提升某几支脚位的静电放电防护能力而已。

IC制程特性有时会有小幅的(10%) 漂移,因此每颗IC之间的特性可能会有些微的不同,其ESD耐压特性也可能会有差异。要有意义的产品品质管制,在一批相同的IC中,要随机取样一些IC做ESD耐压测试,在每样测试中所挑选的IC数目至少大于5颗。在这些ESD耐压测试的IC中,每一颗都可找出该颗IC的ESD failure threshold,可能每一颗之间的ESD failure threshold都不太相同,这时我们定义其中最低的ESD failure threshold为该批IC的ESD failure threshold。当取样的数目越多,该批IC的ESD failure threshold越精确。

由上所述,ESD测试从每一支脚的测试组合,每一颗IC的测试方法,一直到整批IC ESD故障临界电压的判定,都给我们一个很重要的概念,ESD protection不是一支脚的问题,而是整批IC的问题。因此静电放电防护要有效用,就必须考虑到各种ESD情形下,静电放电电流在IC内部流动的路径。