伟芯科技ESD知识分享——制程上(Process Level)的改进方法

伟芯科技(绍兴)有限公司,绍兴集成电路小镇已入住的专业的集成电路静电保护(ESD)技术和IP产品提供商,在ESD保护业务领域积累了丰富的理论基础和实战案例,成功解决了大规模SOC产品、多电源域多管脚产品、RF高频产品、高压产品和finfet等产品的ESD可靠性问题。为广大集成电路企业客户提供ESD IP库开发、全芯片ESD保护方案、ESD失效分析和改进方案、ESD专利授权等产品和服务。

在伟芯官网中,我们将教导您有关集成电路的ESD知识,并介绍集成电路的 ESD 规格标准以及集成电路产品的ESD测试方法;再来,我们将教导您有关集成电路的各种ESD防护设计,其相关技术含括制程 (Process)、元件(Device)、电路 (Circuits) 、系统 (Systems) 、以及测量(Measurement) 。这些相关技术的介绍及设计实例的说明,必能协助您解决贵公司集成电路产品所遭遇到的 ESD问题。

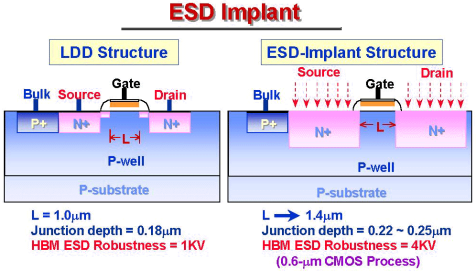

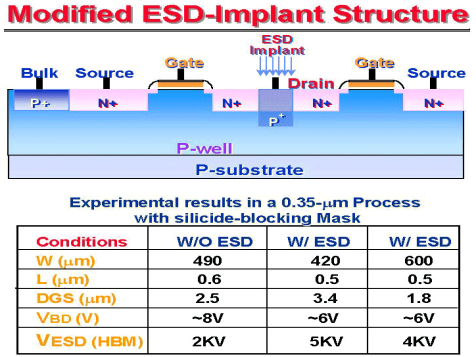

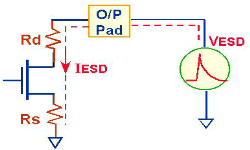

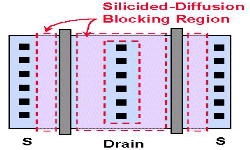

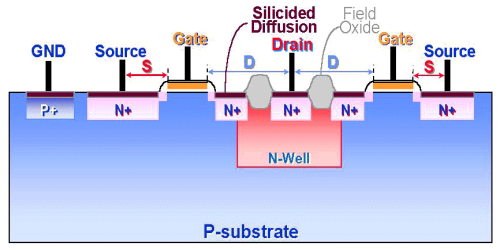

在制程上为加强深次微米CMOS IC的ESD防护能力, 目前发展出两种制程技术以应用于量产制程中。

6.2.1 ESD-Implant Process(防静电放电布植制程)

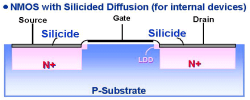

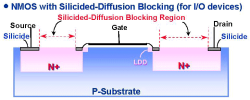

6.2.2 Silicided-Diffusion Blocking Process (金属硅化物扩散层分隔制程)

2020年2月15日 16:58

ꄘ浏览量:0