增强 ESD 能力的方法 - 电路

增强ESD能力 除了工艺以及器件解决方案外,我们还可以使用电路来增强 ESD 能力。栅极接地的NMOS (Grounded-Gate NMOS, GGNMOS) 的结构如图1(a) 所示,NMOS 栅极接地,保证了作为 MOS 管自身不会导通。保护电路利用的 是NMOS横向寄生的npn管,如图1(b)所示,只有当ESD发生时,这个寄生三极管才开启,继而吸收大量电流。

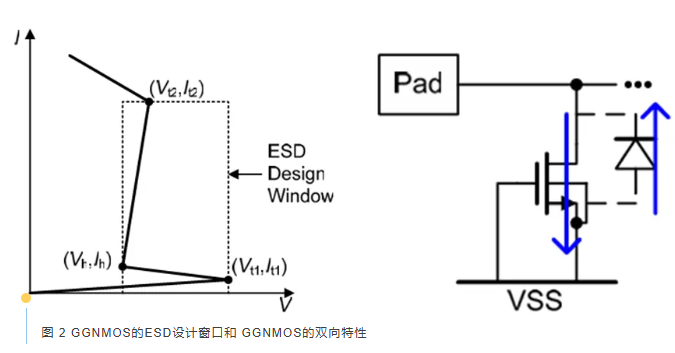

图2给出了GGNMOS的I-V曲线,具体过程如下:

当漏端加ESD正向脉冲 时,漏端n+/p结反偏,器件进入高阻态,直到漏结雪崩击穿,即漏端电压达到一次击穿电压Vt1时,在漏结耗尽区产生电子-空穴对,电子被漏极收集,一部分空 穴被源极收集,剩下的流过衬底。在衬底寄生电阻RSUB上产生电压降,使衬底电压升高,当衬底和源之间的pn结正偏时,NMOS管内部的寄生npn管开启,相 当于发射结正偏,集电极反偏,寄生npn管正向导通,GGNMOS进入微分负阻 区,即电压随着电流增大而下降,漏端电压降至寄生npn管的集电极-发射极导通电压Vh附近。若电流继续上升,电子在源漏之间的电场的作用下被加速,产生电子、空穴的碰撞电离,从而形成更多的电子空穴对,产生局部“热点”,当流过器件漏端的电流密度过大,就会造成热击穿,这是不可回复的损伤。通常漏端的热击穿点位于栅边缘附近,热击穿对应的击穿电压为二次击穿电压Vt2。

作为ESD电源钳位的GGNMOS,必须工作在ESD设计窗口内,要保证电压既不能在正常工作区,也不能达到栅氧击穿区,电流不能超过二次击穿时的It2。 为了增强ESD鲁棒性,即增大ESD设计窗口的面积,可以降低Vt1或者增加It2。 通常使用多指状NMOS以增加晶体管面积来增加It2。 GGNMOS内部有一个寄生的二极管,在反向放电模式时,可以利用这个二 极管。即GGNMOS具有双向性,如图2所示。

图 2 GGNMOS的ESD设计窗口和 GGNMOS的双向特性

上文提及的多指状GGNMOS有一个致命缺陷,当ESD电压来临时,往往出现某个指条首先导通,ESD电流只从该指条释放,特别是如果Vt2小于Vt1,有些指条就可能在其它指条发生骤回现象前二次击穿,降低了多指条晶体管的ESD 性能。这就是为何器件尺寸已经足够大,但ESD保护能力不如预期的原因。

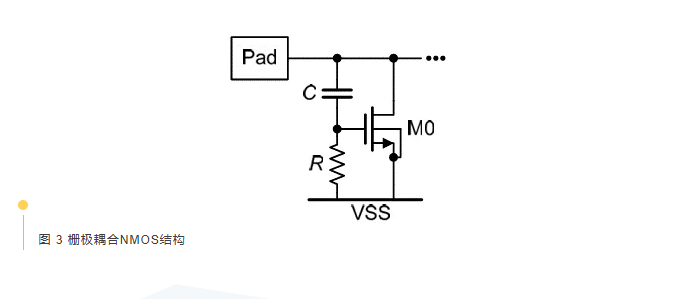

为了提高ESD性能,则需要使其所有指条在ESD应力来临时都导通,我们考虑栅极耦合NMOS (Gate-Coupled NMOS, GCNMOS) 技术。如图 3,电阻R保证该 NMOS在电路正常工作时是关闭的,在ESD发生时,电阻R与MOS寄生电容及外置电容C构成RC结构,电压耦合到NMOS栅极,使它微导通,于是所有指条被一起导通,同时降低了寄生npn管的Vt1,若Vt1<Vt2,就能保证在某个指条进 入二次击穿前,所有指条都已进入骤回区域。

GCNMOS还有一个优点,RC结构使GCNMOS的开启电压很低,在ESD 应力来临的前几ns,电压通过电容C耦合到NMOS的栅极,令栅极为高电平, n 型沟道导通,即使寄生npn没有开启,其本身作为MOS管也能放电一段时间。 需要注意的是,GCNMOS在引脚处安排了额外电容,会严重影响电路的高频特性,在高频电路中使用需格外小心。

粉丝福利(Contact Us)

如果芯片及系统级的ESD/EOS/Latch-up等可靠性問題困扰着您的项目进展,或您想在产品差异性比国际大厂做的好,并且您想在集成电路领域获得升职加薪,别犹豫请私讯我,我手把手教您。

文章转自公众号【电浪 David】 更多专业资讯和技术互动移步联系~