TLP测试的优势-转自电浪David

为什么要做静电测试

在研发出新电子产品后,到量产之前都需先通过许多的测试项,其中HBM与IEC 61000-4-2的测试规范较广为人知,而近年也陆续有厂家指定进行TLP (Transmission Line Pulse) 测试。尽管测试方法有所不同,最终的目的都是为了确保电子产品的可靠度。出厂前经过较严格ESD测试把关的电子产品,其可以应用的范围就较为广泛。不论是处于较潮湿的国家,又或是身在干燥寒冷容易产生静电的地区,都不易受到环境的影响而使消费者的体验上有所不同,如此一来也能增加消费者对品牌的信心。

HBM (器件) 与IEC 61000-4-2 (系统)

HBM仿真人体对器件的放电情形。目前业界IC出厂时大都已经通过HBM的测试。接着到系统组装完成后则会进行IEC 61000-4-2的系统级ESD测试。IEC 61000-4-2的ESD放电RC模型为150pF, 330Ω,而HBM则为 100pF, 1500Ω。由此可得知IEC 61000-4-2的系统级测试拥有较大的充电电容,较小的放电电阻,因此计算下来其测试电流会比HBM高出5倍左右。这也是即使IC出厂时已经通过HBM测试,到组装成系统后却仍需要额外的ESD保护器件 (TVS) 来协助通过IEC 61000-4-2 测试的原因。

TLP测试

TLP测试与HBM及IEC 61000-4-2皆是为了模拟ESD放电的情形。相较于ESD Gun测试只能得知是Pass还是Fail的测试结果,TLP测试会由低电流至高电流进行一次又一次的ESD放电,每次放电时同时量测待测物两端的电压与电流,测试所得之TLP特性图能帮助我们更深入了解TVS在遭遇ESD时的I-V特性与箝制电压 (Clamping Voltage)。

箝制电压即为TVS在遭受ESD冲击时测得的工作电压,因此如果箝制电压越小代表TVS越可能协助代测物通过ESD的测试。此外,可以更进一步比较主芯片与TVS的箝制电压关系,如此将可以预测TVS是否能成功保护主芯片免于ESD能量的破坏,是ESD防护器件最具指针性的参数。

使用 TLP 测试的优势

对单体TVS而言,从做完TLP测试而得的图形之中即可快速的找出在相对应的ESD电流之下,TVS的箝制电压是多少。箝制电压小的TVS代表保护效果更佳,系统越可能通过IEC 61000-4-2的测试。因此TLP图形能协助我们去推测TVS是否能满足系统的ESD防护需求,以通过IEC 61000-4-2的静电测试。

TLP测试的案例

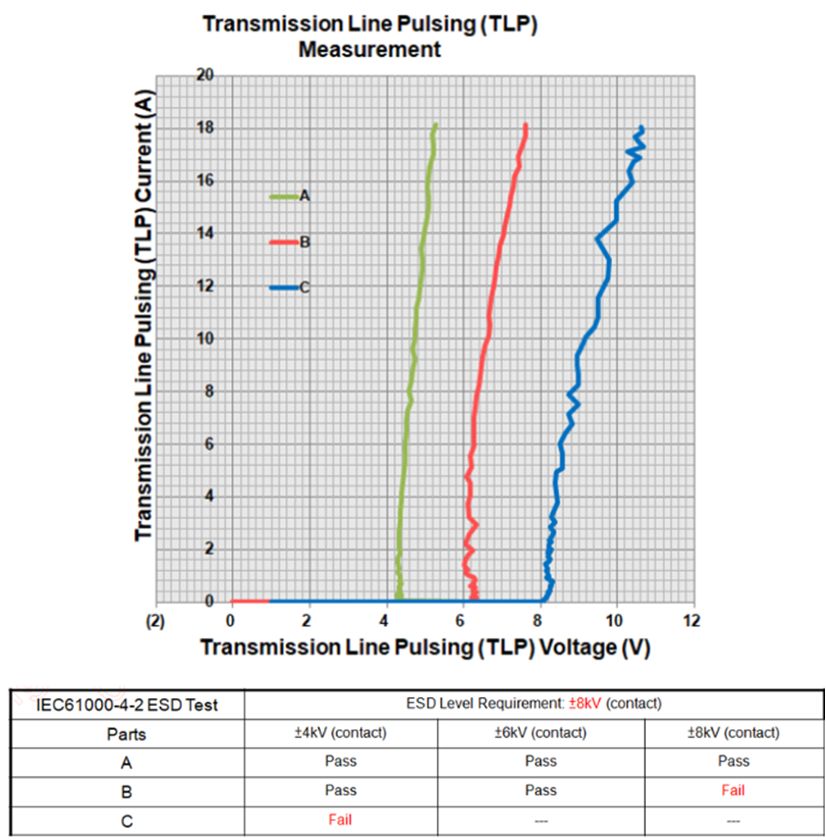

ESD测试Spec为对Desktop的Audio Port 做Contact Discharge 8kV,3颗TVS器件的TLP如图1。此结果说明较低箝制电压的TVS较有可能通过较高Level ESD测试。从TVS箝制电压的比较,也能帮助我们预测IEC61000-4-2的测试结果。

图1 TLP I-V 曲线和IEC 61000-4-2 ESD实测结果。

TLP测试结果解析

当我们在系统上进行TLP测试的时候,我们时常发现若TVS的箝制电压不够低,会导致后方IC损毁而测试Fail,不过TVS却是Pass的情形。这也说明了当我们在挑选TVS的时候,若考虑到TVS的ESD保护能力,应首先注重箝制电压要够低,而非TVS单体的ESD耐受。如此一来就能避免受保护器件Fail,而TVS却未受损的状况,也失去了添加ESD防护器件的目的。搭配TLP特性图来挑选适当的TVS器件,不仅能预防电路中较昂贵的主芯片遭到ESD破坏,同时能提高产品可靠度以减少量产后的客退返修机率,就能避免后续花更多成本来调整电路设计。