高压片内ESD保护器件

高压情况下,需要在一定的电压范围内控制器件的触发电压和维持电压,以保证其具有好的ESD特性。ESD保护器件的触发电压Vt1应该比内部器件的结击穿电压和栅氧击穿电压小,这样可以更有效的保护内部电路。而维持电压Vh应比工作电压VDD大,抑制闩锁效应。正是由于功率集成电路中的VDD比较高从而给高维持电压的ESD保护器件设计带来了挑战。

在低压集成电路中,SCR管以其高效的ESD泄放表现广泛的作为ESD保护器件使用。但是常规SCR具有很强的回滞特性,触发电压高,维持电压低的特点使其在高压ESD保护中难以发挥其ESD防护的优势。下面提出一种改进的SCR结构使其适应于高压ESD片内防护的设计要求。

这里具体分析提高MLSCR器件高压ESD保护特性的器件结构。

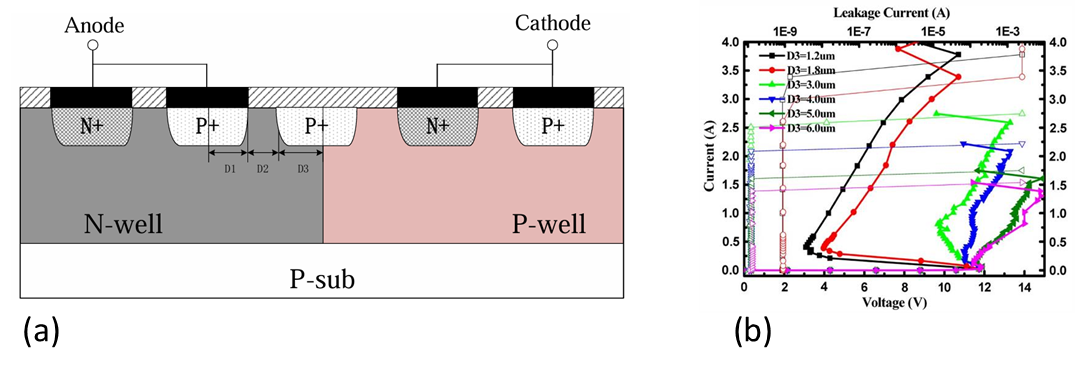

图1(a) 给出了MLSCR的横向截面示意图

图1(b) 给出了不同D3值的MLSCR器件TLP测试结果

图1 (a) MLSCR 结构图,(b) 不同D3值的MLSCR器件TLP测试结果。

与普通结构的LSCR相比,MLSCR在P-well与N-well 区域之间增加了一块 P+区域,这样在MLSCR的阳极与阴极之间加上正向的ESD脉冲时,其触发电压由原来的N-well/P-well 雪崩击穿结变为P+/N-well结,这明显降低了MLSCR的触 发电压。但是这一结构对 MLSCR 的维持电压并无太大影响。为了进一步提高 MLSCR的维持电压,D3的增加可以增加维持电压,同时对器件的触发电压几乎无影响。

图1(b) 给出了几种不同MLSCR器件结构(D1均为1.6 μm,D2均为0.6 μm, D3 的值不同)的TLP结果。从图中可以看出,随着D3从1.2 μm增加到6.0 μm,维持电压从3 V增加到11.5 V, 然而触发电压基本无变化。同时,随着维持电压的增加,失效电流It2自然地会跟着下降,所以维持电压的增加是以牺牲ESD泄放性能为代 价的。

优化设计了小回滞特性的MLSCR器件结构以后,还可以通过MLSCR 的堆叠结构进一步增加高压 ESD 防护应用中的维持电压。

高压 ESD 防护的另一难点就是维持电压要高,除了上述增加单个 MLSCR器件的维持电压外,还可以通过器件堆叠的方式进一步增加维持电压,堆叠方法的优势就是对失效电流的影响较小。图2(a) 给出了两个MLSCR单元串联堆叠结构示意图,图2(b) 给出了不同MLSCR堆叠个数时的TLP测试I-V曲线图。

图2 (a) 两个MLSCR堆叠结构示意图,

(b) 不同MLSCR堆叠时的TLP测试I-V曲线图。

图2(b) 给出了D3为4 μm的MLSCR堆叠个数分别为1、2、3、4个时的TLP 测试I-V曲线图。从图中可以明显看到维持电压随器件堆叠数目而成倍增加,失效电流只是略有下降。当堆叠个数为4个时,触发电压为47 V左右,而维持电压高达44 V左右,回滞量只有3 V,失效电流为2.3 A左右,超过3 KV的HBM耐压等级。当需要更高维持电压的应用时,只需增加MLSCR的堆叠数目即可。

*文章转自--电浪David